## **CMOS Logic Circuits:**

## CMOS NOR2 (Two-Input NOR) Gate:

The output voltage of the CMOS NOR2 gate will attain a logic-low voltage of  $V_{OL}$ = 0 and a logic-high voltage of  $V_R$  =  $V_{DD}$ . For circuit design purposes, the switching threshold voltage  $V_{th}$  of the CMOS gate emerges as an important design criterion. We start our analysis of the switching threshold by assuming that both input voltages switch simultaneously, i.e.,  $V_A$  =  $V_B$ .

$$V_{th}(NOR2) = \frac{V_{T,n} + \sqrt{\frac{k_p}{4k_n}} \left(V_{DD} - |V_{T,p}|\right)}{1 + \sqrt{\frac{k_p}{4k_n}}}$$

we can easily derive simple design guidelines for the NOR2 gate. For example, in order to achieve a switching threshold voltage of  $V_{DD}/2$  for simultaneous switching, we have to set  $V_{T,n} = |V_{TP}|$  and  $k_p = 4 \ k_n$ .

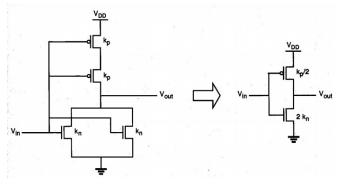

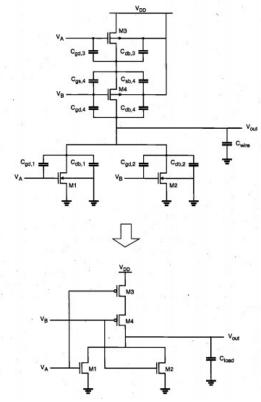

Figure shows the CMOS NOR2 gate with the parasitic device capacitances, the inverter equivalent, and the corresponding lumped output load capacitance. In the worst case, the total lumped load capacitance is assumed to be equal to the sum of all internal parasitic device capacitances seen in Fig.

**Fig.** Parasitic device capacitances of the CMOS equivalent with the lumped output load capacitance. NOR2 circuit and the simplified

## CMOS NAND2 (2-Input NAND) Gate:

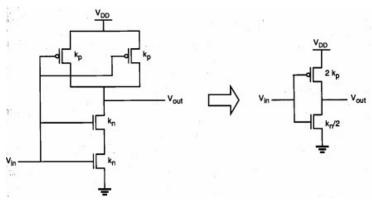

Figure shows a two-input CMOS NAND (NAND2) gate. The operating principle of this circuit is the exact dual of the CMOS NOR2 operation examined earlier. The n-net consisting of two series-connected NMOS transistors creates a conducting path between the output node and the ground only if both input voltages are logic-high, i.e., are equal to  $V_{OH}$ . In this case, both of the parallel-connected PMOS transistors in the p-net will be off. For all other input combinations, either one or both of the PMOS transistors will be turned on, while the n-net is cut-off, thus creating a current path between the output node and the power supply voltage.

Using an analysis similar to the one developed for the NOR2 gate, we can easily calculate the switching threshold for the CMOS NAND2 gate. Again, we will assume that the device sizes in each block are identical, with  $(W/L)_{n,A}=(W/L)_{n,B}$  and  $(W/L)_{P,A}=(W/L)_{p,B}$ . The switching threshold for this gate is then found as

$$V_{th}(\text{NAND2}) = \frac{V_{T,n} + 2\sqrt{\frac{k_p}{k_n}} \left(V_{DD} - \left|V_{T,p}\right|\right)}{1 + 2\sqrt{\frac{k_p}{k_n}}}$$

Fig. A CMOS NAND2 gate and its inverter equivalent

A switching threshold voltage of  $V_{DD}/2$  (for simultaneous switching) is achieved by setting  $V_{T,n} = |V_{T,p}|$  and  $k_n$ =4 $k_p$  in the NAND2.